Keysight PLTS 2024安装包免费下载 安装教程

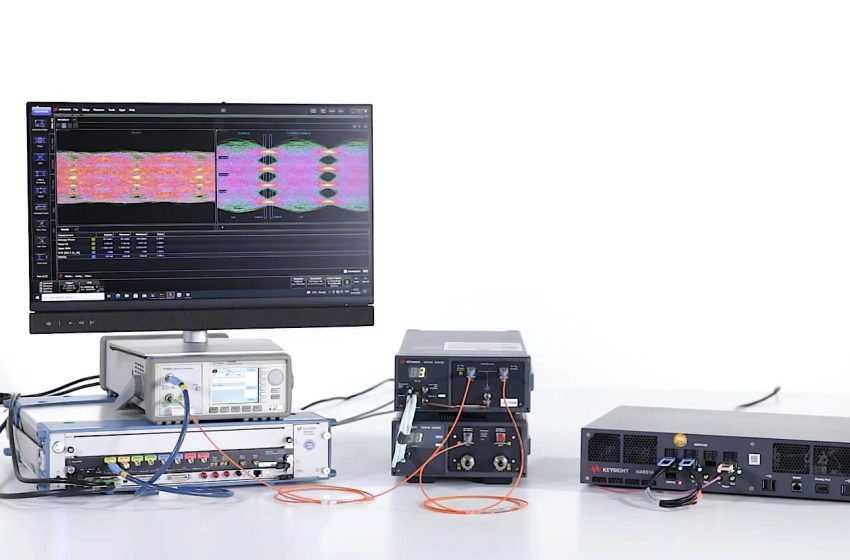

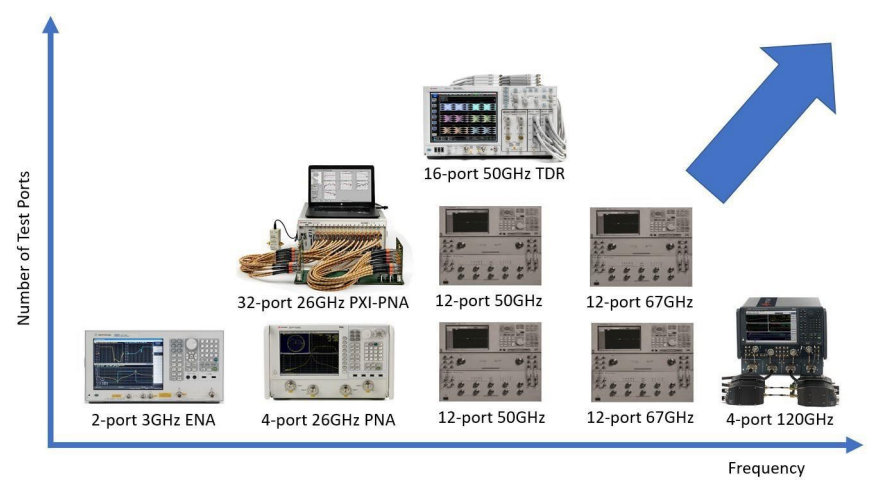

物理层测试系统(Physical Layer Test System PLTS)是对电缆、背板、印刷电路板和连接器等高速互连器件进行信号完整性测量和数据后处理的行业标准。全球许多信号完整性实验室在研发原型测试阶段都受益于 PLTS 的强大功能。 如今,1.6 Tbps 的互联系统需要进行多端口信道分析,以减少可能导致误码的串扰问题。新型 PLTS 2024 现已升级为功能强大的 64 位应用程序,可为大型数据文件提供更深的内存,并实现 16 端口 或 32 端口 S 参数测量。

目前正在开发的下一代计算机和通信系统将处理每秒数十G比特的数据速率。许多系统将采用超过GHz时钟频率的处理器和 SERDES 芯片组。随着交换机、路由器、服务器刀片和存储区域网络设备向 800 Gbps 数据传输速率发展,新的、令人头疼的输入/输出问题正在出现。为这些系统选择芯片到芯片、芯片到模块和背板技术的数字设计工程师发现了前所未有的信号完整性挑战。

传统的并行总线拓扑已经耗尽了带宽。随着并行总线的位宽越来越宽,在 PCB 上布线的复杂性和成本也大幅增加。在并行总线中,数据线和时钟线之间的偏移越来越大,越来越难以解决。解决方案就是采用高速串行通道。在高速数字系统中,较新的串行总线结构已迅速取代并行总线结构。工程师们已经开始采用多种具有嵌入时钟功能的Gbps串行互连协议,以实现简化布线和具有更大传输带宽的目标。然而,这些串行差分互连也带来了一系列问题。

为了保持与老式并行总线相同的总带宽,新的串行总线需要提高数据传输速率。随着串行互连数据速率的提高,数据从逻辑0电平转换到逻辑1电平的上升时间也会变短。这种较短的上升时间会在阻抗不连续处产生较大的反射,并降低通道末端的眼图质量。因此,印刷电路板走线、连接器、电缆和集成电路封装等物理层元件再也不能被忽视。事实上,在许多情况下,硅的速度非常快,物理层器件已成为瓶颈。

为了在整个通道中保持信号完整性,工程师们正在摒弃单端电路,转而使用差分电路。差分电路具有良好的共模抑制比 (CMRR),有助于屏蔽相邻 PCB 线路的串扰。设计合理的差分传输线路可最大限度地减少模式转换的不良影响,并尽可能提高最大数据传输速率。遗憾的是,差分信号技术并不总是一门直观的科学。

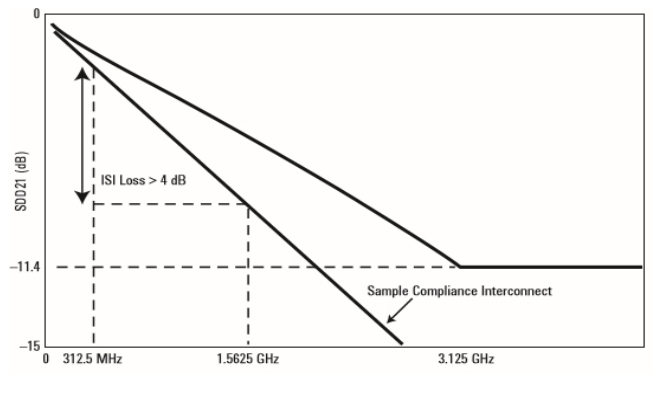

目前,许多数字标准都使用频域测量来进行合规性测试,如上图的输入差分插入损耗 (SDD21) 掩图模板所示。

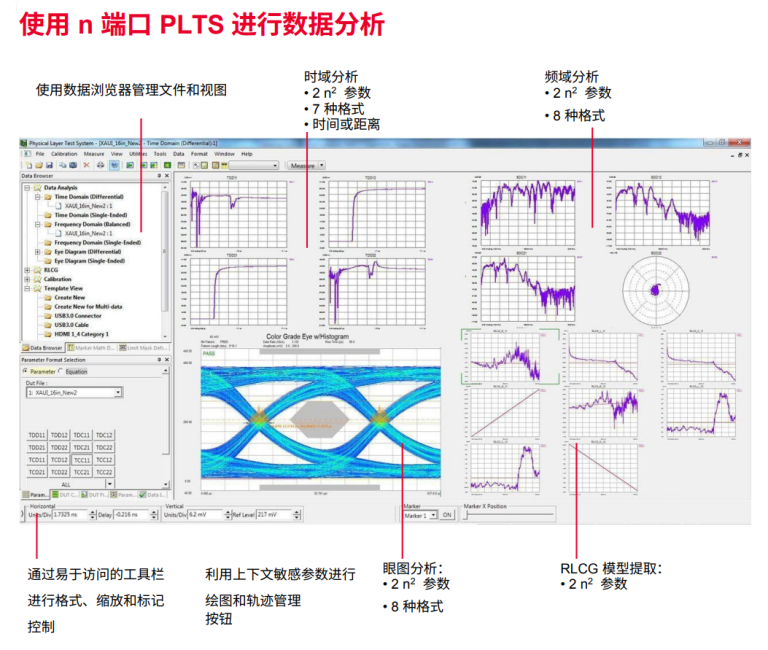

PLTS 单个测试系统可提供全面的视

随着时域和频域分析的结合变得越来越重要,对多个测试系统的需求也变得难以管理。能够全面鉴定差分高速数字设备,同时将分析的域和格式留给设计人员的单一测试系统是非常强大的工具。

Keysight 的物理层测试系统 (PLTS) 就是专门为此目的而设计的。 PLTS 专为信号完整性分析而设计。PLTS 软件可指导用户进行硬件设置和校准,并控制数据采集。它能自动应用获得专利的转换算法,以频域和时域、正向和反向传输和反射以及所有可能的工作模式(单端、差分和模式转换)显示数据。 强大的虚拟比特模式生成器功能允许将用户定义的二进制序列应用于测量数据,以卷积眼图。

接下来,可以提取高精度的 RLCG 模型,用于提高模型和仿真的精度。虽然 PLTS 主要是一种研发工具,但其 SCPI 接口具有丰富的命令集,可用于远程测量和制造应用。此外,制造应用还可受益于 PLTS 内部的定制表征报告 ,该报告允许用户自动记录所需的所有多领域数据。

PLTS 通过完整的特征描述为设计提供信心

物理层结构日益成为高速数字系统性能的瓶颈。在低数据速率情况下,这些互连可视为电气短路的,其对信号传输性能的影响可以忽略不计,驱动器和接收器通常是影响信号完整性的最大因素。

但是,随着时钟速度、总线速度和链路速度都突破每秒千兆位大关,物理层鉴定变得更加重要。这些互连线变成了微波传输线,需要仔细鉴定,以避免互联出现问题。 当今数字设计人员面临的另一个挑战是采用差分拓扑结构的趋势。要充分了解器件的性能,需要对所有可能的工作模式进行分析。

时域分析通常用于鉴定这些物理层结构,但设计人员往往只关注预期的工作模式。要获得完整的时域视图,必须查看反射和透射(TDR 和 TDT)的阶跃和脉冲响应。分析还必须包括非预期工作模式。 要全面鉴定这些物理层结构,还必须在所有可能的工作模式下进行频域分析。

s 参数模型描述了这些数字结构的模拟行为。这种行为包括不连续性反射、频率相关损耗、串扰和 EMI 性能。 为了将器件性能转化为标准合规性,眼图增加了一项重要的统计分析。为了将完整的特性分析应用到改进的仿真中,基于测量的 s 参数或 RLCG 模型提取可完善整个过程。

PLTS 可进行模式转换分析,及早发现 EMI 问题

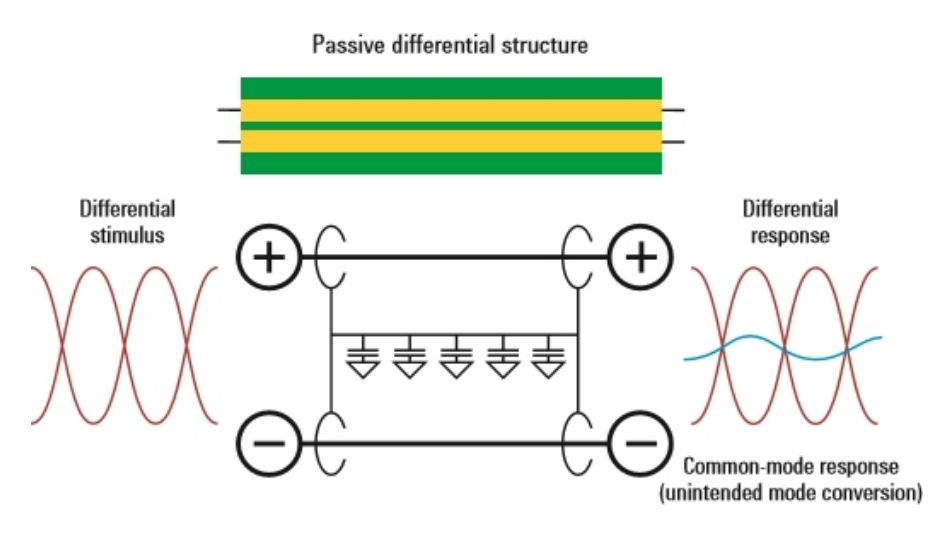

差分信号的优点包括电压波动更小、抗电源噪声、减少对射频接地的依赖以及改善 EMI 性能。器件利用这些优势的程度与器件对称性直接相关。 对称器件只响应和产生差分信号。这些理想器件不会响应或产生共模信号,并能抑制外部辐射信号(即电源噪声、数字时钟或数据的谐波以及来自其他射频电路的 EMI)。

然而,非对称器件并不具备这些优势。当受到差分激励时,非对称器件除了产生预期的差分响应外,还会产生共模响应,并导致 EMI 辐射。

相反,在共模刺激下,非对称器件会产生非预期的差分响应。这种模式转换是 EMI 易感性的来源。 模式转换分析是了解和改进器件对称性的重要工具,它为设计人员在设计阶段识别和解决 EMI 问题提供了早期洞察力。

PLTS 2024 有哪些新功能?

现在使用 PLTS N19308B 选项计算表面粗糙度 (Rz)

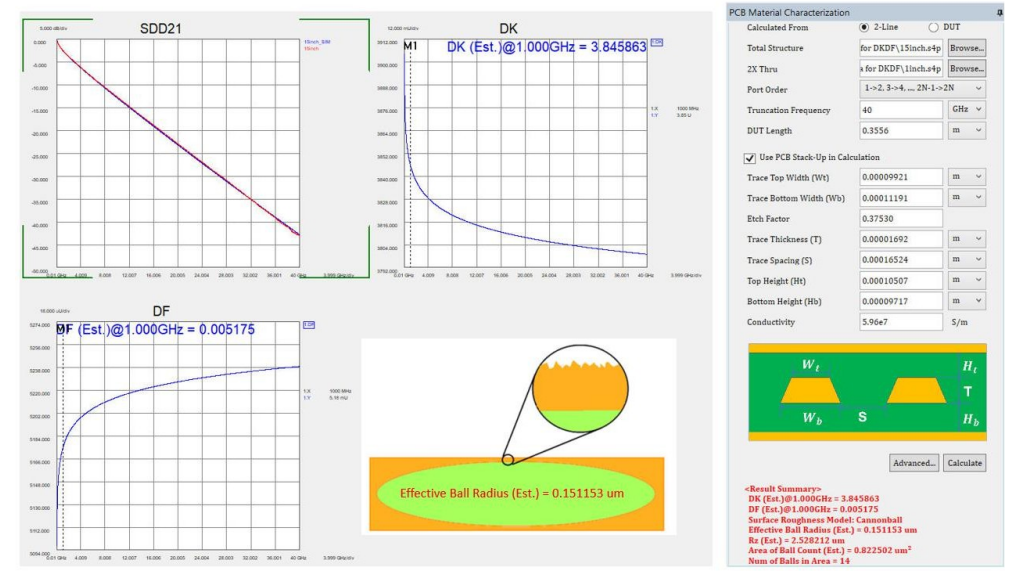

由于数据在超高速 PC 电路板上传输时会产生信号损耗,高速数字设计面临着巨大挑战。当所谓的相同印刷电路板显示出不同的电气性能时,问题往往可以追溯到印刷电路板材料本身的基本属性(即铜表面损耗和 Dk/Df)。

通过使用新的 PLTS 2024 PCB 材料测量软件,信号完整性工程师现在可以对介电材料特性进行有价值的分析。较高的铜粗糙度会阻碍电流流动,导致较高的插入损耗。通过从电路板设计中提取这一关键参数,现在可以发现材料问题。

PLTS 2024 PCB 材料特性软件模块可提取关键的 PCB 信息,用于优化高速数字设计

计算插入损耗/英寸的 Delta-L(1L/2L/3L)方法

先进的去嵌工具,如 Keysight 的自动夹具移除 (AFR) 可以实现无与伦比的精确提取模型。但是,如果需要更简单的去嵌工具,则可以轻松使用英特尔的 Delta-L 方法。随着越来越多的 PCB 制造商在电路板上集成高速 Tx/Rx 芯片组,测量和控制基于频率的损耗的需求也随之增加。测量传输线损耗给制造商带来了 一系列与验证阻抗截然不同的挑战。PLTS 2024 版本中包含的 Delta-L 1 线、2 线和 3 线方法是行业标准之一,可用于在当今较高数据速率下简单、快速地确认印刷电路板性能。

如何安装PLTS 2024

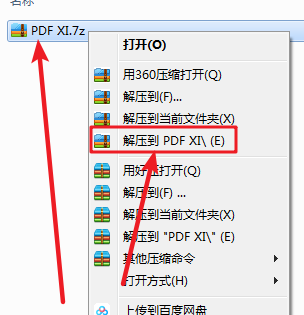

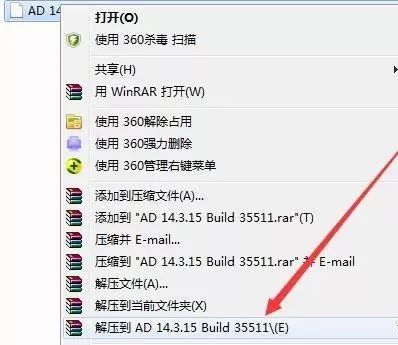

软件安装比较简单,网盘内的PLTS2024U1_64bit_Full_Install.zip是主程序的安装包,下载下来并解压,运行其中的setup.exe启动安装向导,按正常流程安装PLTS 2024即可,基本上就是一路next即可。

安装完成后,将网盘内的PLTS2024U1_PatchFiles.zip解压出来,然后将其拷贝到PLTS的安装后的路径下,也即是会覆盖同名的PLTS2024U1文件夹内的同名文件,最后再运行一下PLTSLicenseSetup.exe即可完成激活。

下载仅供下载体验和测试学习,不得商用和正当使用。